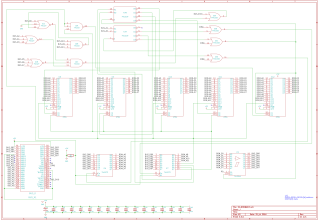

(クリックで拡大)

(クリックで拡大)論理的に間違ってるとかあったら、ツイッターとかで教えてください(@morian)。プルリク出してもらえると嬉しいです。

配線が雑なのは許してください。

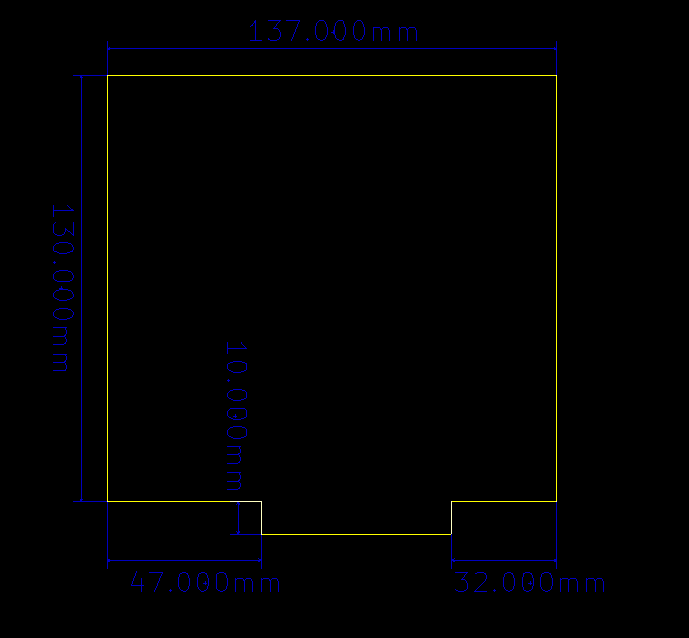

以下の場所に、KiCad用のプロジェクト一式を置いてあります。回路図をおこしてフットプリントの作成までしてみました。(作り方が適切かどうかはわかりません)

てきとーに測りました。実物は角の部分がマルッとしてます。外形図なのでエッジコネクタ部分の金属端子までの余白があります。

基板の厚さは1.6mmです。

ボード上のROMがZ80空間に配置されるのではなく、X1本体側(Z80側)から、I/Oポートを通して1バイト単位でボード上のROMから読み込みを行います。

| I/Oポート | 用途 |

|---|---|

| 0E00h | アドレス上位 |

| 0E01h | アドレス中位 |

| 0E02h | アドレス下位 |

| I/Oポート | 用途 |

|---|---|

| 0E03h | 指定されたアドレスのデータ |

IPL ROMは電源投入時にBASIC ROMボード上のアドレス000000Hから1バイト読み込みし、それが01HであればBASIC-ROMボードにアクセスできるものと判定し、BASIC-ROMからプログラムを読み込み、実行を開始します。

BASIC-ROMボードからのプログラム読み込み処理は以下の流れになります。

BASIC-ROM上の最初の20hバイト分は以下の内容になっています。

| アドレス | 用途 | データ | ASCII |

|---|---|---|---|

000000h |

CHECK用 | 01h |

|

| 000001h | 起動メッセージ | 42h | B |

| 000002h | 41h | A | |

| 000003h | 53h | S | |

| 000004h | 49h | I | |

| 000005h | 43h | C | |

| 000006h | 20h | ||

| 000007h | 43h | C | |

| 000008h | 5Ah | Z | |

| 000009h | 38h | 8 | |

| 00000Ah | 52h | R | |

| 00000Bh | 42h | B | |

| 00000Ch | 30h | 0 | |

| 00000Dh | 31h | 1 | |

| 00000Eh | 20h | ||

| 00000Fh | 20h | ||

| 000010h | 20h | ||

| 000011h | 20h | ||

| 000012h | 読込む長さ | 00h | |

| 000013h | A6h | ||

| 000014h | Z80側読込み先 | 00h | |

| 000015h | 00h | ||

| 000016h | Z80側開始アドレス | 00h | |

| 000017h | 00h | ||

| 000018h | 20h | ||

| 000019h | 20h | ||

| 00001Ah | 20h | ||

| 00001Bh | 20h | ||

| 00001Ch | 20h | ||

| 00001Dh | BASIC ROM読込み元アドレス |

20h | |

| 00001Eh | 00h | ||

| 00001Fh | 00h |

| アドレス | 用途 |

|---|---|

| 0000 | ユーザI/Oポート |

| 0FFF | |

| 1000 | システムI/Oポート |

| 1FFF | |

| 2000 | 属性V-RAM |

| 27FF | |

| 3000 | テキストV-RAM |

| 37FF | |

| 4000 | GRAPHIC V-RAM1(B) |

| 7FFF | |

| 8000 | GRAPHIC V-RAM1(R) |

| BFFF | |

| C000 | GRAPHIC V-RAM1(G) |

| FFFF |

拡張I/Oポートコネクタピン配置図(本体後面側から見た図)

| A側(上部) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| B側(下部) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

※X1Cのマニュアルでは端子番号の並びが左右逆になっています。

| 端子番号 | A側信号名 | B側信号名 |

|---|---|---|

| 1 | Vcc1 | Vcc1 |

| 2 | DB2 | DB3 |

| 3 | DB1 | DB4 |

| 4 | DB0 | DB5 |

| 5 | GND | DB6 |

| 6 | AB15 | DB7 |

| 7 | AB14 | CPU CLK |

| 8 | AB13 | ^M1 |

| 9 | AB12 | ^WR |

| 10 | AB11 | ^RD |

| 11 | AB10 | ^IORQ |

| 12 | AB9 | ^MREQ |

| 13 | AB8 | GND |

| 14 | AB7 | ^HALT |

| 15 | AB6 | IEI |

| 16 | AB5 | N.C. |

| 17 | AB4 | RESET |

| 18 | AB3 | ^EXIO |

| 19 | AB2 | ^EXINT |

| 20 | AB1 | ^EXWAIT |

| 21 | AB0 | ^NMI |

| 22 | GND | GND |

| 信号名 | 論理 | 用途 |

|---|---|---|

| DB0-7 | 正 | データバス |

| AB0-15 | 正 | アドレスバス |

| CLK | 単相4MHzのクロック出力 | |

| ^M1 | 負 | Z80 M1 |

| ^WR | 負 | Z80 WR |

| ^RD | 負 | Z80 RD |

| ^IORQ | 負 | Z80 IORQ |

| ^MREQ | 負 | Z80 MREQ |

| ^HALT | 負 | Z80 HALT |

| IEI | 正 | 割込みイネーブル入力信号 |

| RESET | 正 | Z80 HALT |

| ^EXIO | 負 | 0000h-0fffhまでのアドレスデコード出力 |

| ^EXINT | 負 | 外部機器からの割込み要求信号 |

| ^EXWAIT | 負 | 外部機器からのウェイト信号 |

| ^NMI | 負 | 外部機器からのNMI割込み要求信号 |

電源投入時(IPL起動時は)、Z80メモリ空間の0000-0FFFhに4KByteのIPL ROMが配置され、メモリからの読込みはIPL ROM、書込みはRAMになります。また、この時のメモリ読み込み動作はWAITが1つ挿入されます。8000-FFFFhへの読み書き先はRAMになります。

IPLからシステムが以降すると、IPLはZ80メモリ空間から切り離され、RAM全領域(64KByte)への読み書きとなります。